fujiwaraさんの所で、Silicon LabsのSi5317を使用したジッタクリーナがリリースされた。

これに使われているチップは、ジッタをfs(フェムト秒)レベルまで減少させるという。

Si5317の説明を見るとDSPLLというのがキモのようだが、どういったものだろう?

ちょっと調べてみたところ、同社の水晶発振器にもDSPLLが使われており、原発振は固定周波数、DSPLLの設定で出力周波数を設定(固定値)、ジッタが0.3ps以下というのが売り。

どうやら、高精度&低雑音のPLLということらしい。

となると構成図から考えてもSi5317は、入力されたクロックを、高精度&低雑音のDSPLLで打ち直す物と考えて良さそうだ。

って事は、水晶発振器の出力(もしくはPLLの出力)をこれに通せば、低ジッタの発振器(もしくはPLL)に交換したような効果が得られるということで、結構応用が効きそうだなぁ。

なにはともあれ、入手して作成開始。

今回頒布されたものは、Si5317をはじめロジック系のチップは全て入っているので、部品の収集が簡単である。

入手し辛い部品が無いように、よく考慮されており、作る側としては非常にありがたい。

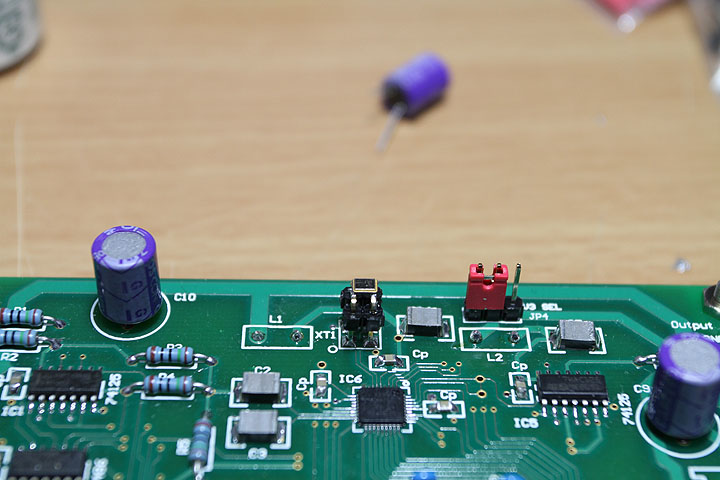

今回メインのSi5317は36ピンのQFNタイプ。

今までハンダ付けしたことのない種類のパッケージであるが、意外とあっさりハンダ付けできた。(あまりハンダを流し込みし過ぎない限り大丈夫だろう。)

それよりてこずったのは、プルアップ・ダウン用のチップ抵抗。

ちょっと大きめの蚤か?と思うぐらいのサイズなので、かなり大変。

結局作業中、三つほど行方不明になってしまった(笑)

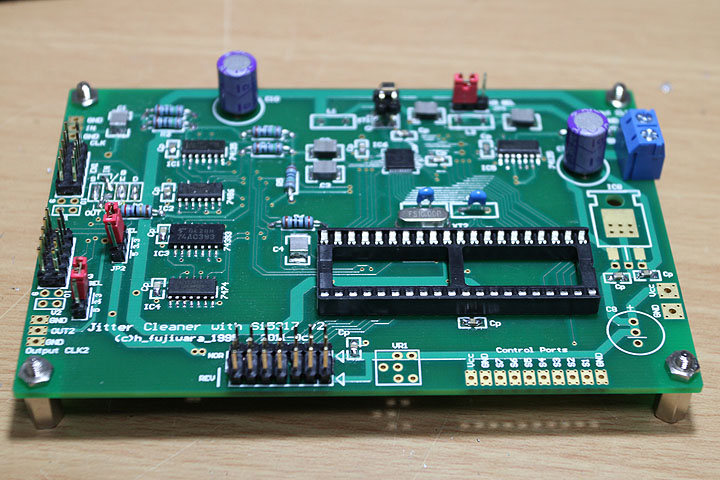

ということで、出来上がり。

今回3.3V専用で作ったので、レギュレータは未実装。

メリットがあるかどうかわからないが、Si5317用の表面実装用水晶は、交換可能なように怪しげなタワーの先に取り付けてある。(Si5317の構造上、周波数安定度以外は水晶交換のメリットは少なそうだ。)

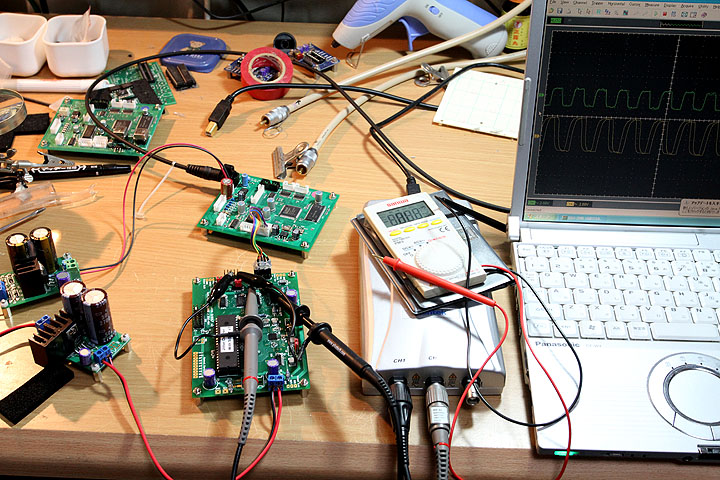

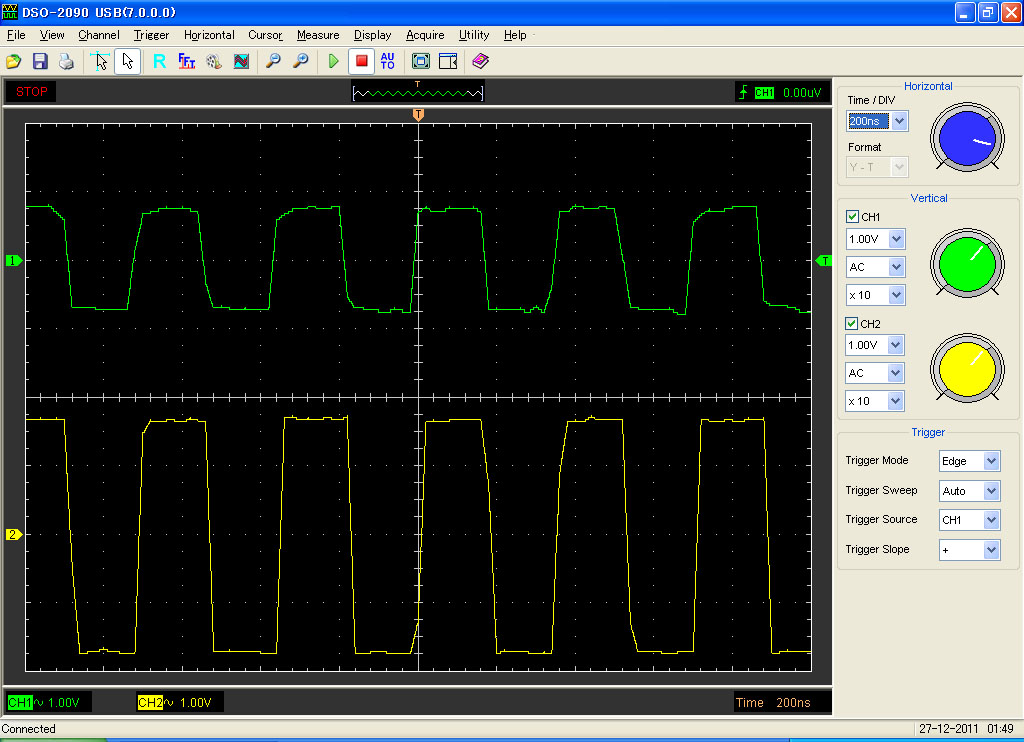

ということで、SD-RAM-DAIと接続し、BCKをクリーニングする設定にして動作確認。

ありゃ?

信号は出ているものの、入力信号と位相が一致しない。

ステータスを確認すると「位相微調整中」のままだ。

なんか間違えたかな?

そういえば、Si5317の背面のパッドにきちんとはんだが流れ込んでいないと安定しないって話があったな。

ということで、再度Si5317の背面の部分のハンダ付けのし直し。

今度は問題無く位相調整が動作し、ステータスも「PLLロック状態、位相微調整停止」になった。(192kHzでも数秒で位相調整完了。)

結構熱をかけたつもりだったんだが、甘かったらしい。

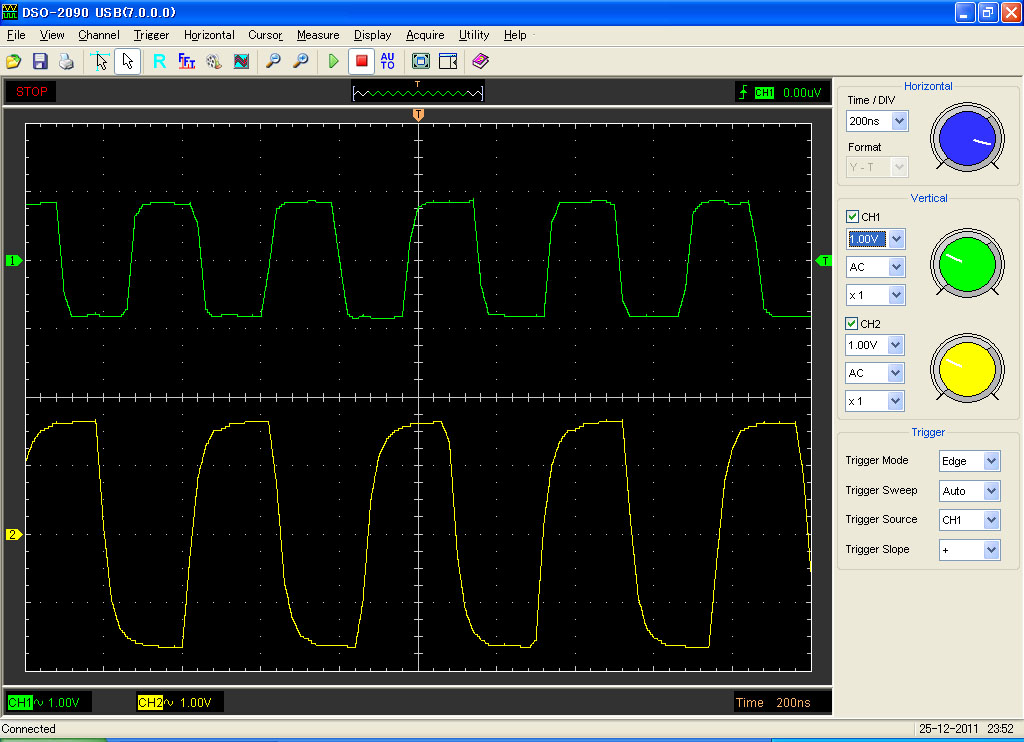

しかし、SD-RAM-DAIの信号は初めて見たが、結構綺麗な波形だね。

Si5317の出力は、振幅が大きくなっているものの、波形的にはあまり変わらない…かな?

さて、何に組み込んで試聴するかな?